I am a fist-year PhD student at University of Edinburgh(UoE), UK. I got my Master degree from Eindhoven University of Technology(TU/e), Netherlands and my bachelor degree from Hefei University of Technology(HFUT), China. My research focuses on designing digital hardware acceleration systems for large-scale AI models using novel architectures, aiming to overcome memory and computational bottlenecks. My current focus is on advancing hardware accelerators for LLMs, VLMs, and generative AI to enable next-generation intelligent computing.

Here is my CV, and I am looking for possible research collaboration. If you are interested in me, please feel free to contact me at any time.

🔥 News

- [2025.07] [Paper] Our work "LinkBo: a Single-Wire, Low-Latency, and Robust Protocol for Variable-Distance Chip-to-Chip Communications" accepted to SOCC 2025 and selected as oral presentation.

- [2025.01] 🎉🎉 I started my PhD study in University of Edinburgh, supervised by Dr. Shady Agwa and Professor Themis Prodromakis.

- [2024.11] 🎉🎉 I finished my internship at NXP Semiconductors and successfully defenced my Master Thesis with 8.5/10 at TU/e. Committee member: Marc Geilen, Manil Dev Gomony and Chengmin Li.

- [2024.09] 🎉🎉 I got a conditional PhD offer at the University of Edinburgh.

- [2024.03] 🎉🎉 Congratulations Intrinsic ID is acquired by Synopsys.

- [2024.03] 🎉🎉 I change my master thesis to NXP Semiconductors in Nijmegen, supervised by Kimmo Salo(NXP), Gustavo Naspolini(NXP).

- [2023.11] 🎉🎉 I started working as a Oversea VC Intern(Remote) at Linear Capital.

- [2023.10] 🎉🎉 I finished my internship at Intrinsic ID and got 8.5 of internship. I also start my research on Neuromorphic at TU/e.

- [2023.07] 🎉🎉 I will be an intern at Intrinsic ID for 3.5 months, supervised by Rui Wang(Intrinsic ID), Roel Maes(Intrinsic ID) and Manil Dev Gomony(TU/e & Nokia Bell Labs).

- [2022.09] 🎉🎉 I started my master's study at Eindhoven University of Technology (TU/e), The Netherlands.

- [2022.07] 🎉🎉 I am graduated from Hefei University of Technology with a bachelor degree, supervised by Zhenmin Li.

📝 Publications

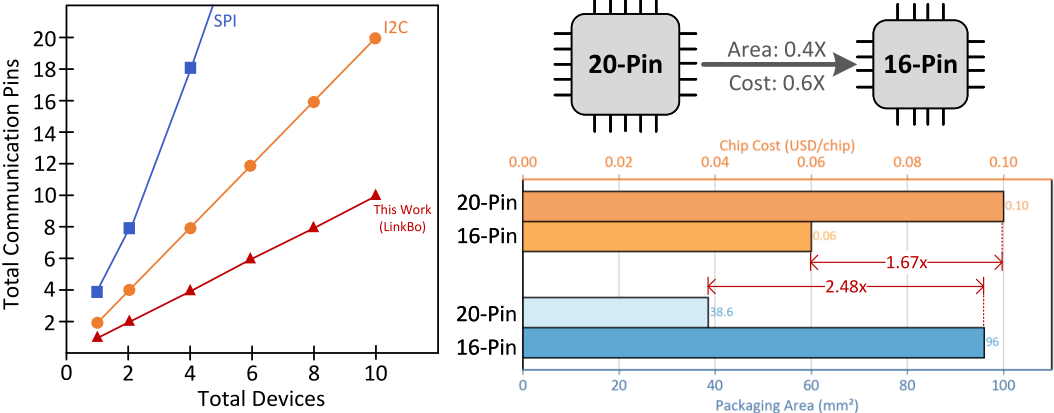

LinkBo: a Single-Wire, Low-Latency, and Robust Protocol for Variable-Distance Chip-to-Chip Communications

Bochen Ye(TU/e & NXP), Gustavo Naspolini (NXP), Kimmo Salo (NXP), Manil Dev Gomony (TU/e)

IEEE International System-on-Chip Conference (SOCC), 2025

Selected as Oral Presentation and Student Contest

Paper/Slides/Poster/ArXiv(Full Version)

We propose LinkBo, a single-wire communication protocol with dedicated hardware architecture, designed to achieve low latency (50.4 µs), high throughput (up to 7.5 Mbps @ 11 cm and 300 kbps @ 15 m), and robust priority-aware delivery.

🏫 Educations

2025.01-Now, University of Edinburgh, United Kingdom

- PhD student of Engneering

- Advisors: Professor Themis Prodromakis and Dr. Shady Agwa

- Research interest: Digital Hardware Accelerator for Generative AI.

2022.09-2024.11, Eindhoven University of Technology, The Netherlands

- Msc.Eletrical Engneering(track:Electronic System)

- GPA: 7.8/10

- Relevant Course: Digital integrated circuit design, Embedded computer architecture, Electronic design automation, Applied combinatorial algorithms, Intelligent architectures(focus on DNN/Hardware co-design), Systems on silicon(focus on SoC backend), Neuro computation(focus on Neuromorphic computing).

- Thesis: LinkBo: A Robust Low-Latency 1-Wire Protocol for Chip-to-Chip Communications (8.5/10)

2018.09 - 2022.07, Hefei University of Technology, China

- Bachelor in Integrated Circuit Design and Integrated Systems

- GPA: 83.1/100 (TOP 22%)

- Relevant Course: Analysis and Design of Integrated Digital Circuit, Microprocessor architecture and design, Introduction to SoC design, Verilog HDL and FPGA implementation and so on.

- Thesis: The Research and Implementation of Router for Packet-Connect-Circuit Network-on-chip

💻 Internships

2024.03 - 2024.10, NXP Semidocutors, Nijmegen NL

-

Digital Design Intern

I am working in AA-APS, this thesis project supervised by Kimmo Salo(NXP), Gustavo Naspolini(NXP), and Manil Dev Gomony(Bell Lab & TU/e). My work as follow:

- Define a custom 1-wire digital communication protocol between two ICs.

- Develope high-level model in Simulink and test the channel model with parasitic parameter.

- Develop and verify an IP module implementing the new communication protocol using SystemVerilog.

- Use Cadence Xcelium to simulate, Cadence SimVision to see the wave, Cadence Conformal Lint to lint and DesignSync to verision control.

- Build a prototype demonstrator with 2 FPGAs.

2023.11 - 2024.06, Linear Capital, China (Remote Part-time)

-

Oversea VC Intern

During my internship at Linear Capital, my responsibilities included:

- Mapping overseas talent in the academic and industrial sectors, providing vital insights for project recruitment and business collaborations.

- Conducting assessments for the commercialization and implementation of potential projects, analyzing market opportunities and risks to support investment decisions.

- Participating in the planning and execution of early-stage investments, collaborating with startups to drive project success.

2023.07 - 2023.10, Intrinsic ID(Now acquired by Synopsys), Eindhoven NL

-

IP Modeling and Digital IC Design Intern

I worked in Research and Security Department(now SoC Security of Synopsys). This internship supervised by Manil Dev Gomony(Bell Lab & TU/e) and Rui Wang & Roel Maes(Intrinsic ID). My work as follow:

- Study on a trellis-based Reed-Muller codec.(Algorithm)

- Use Python modeling it as a digital IP module.(software)

- Design the architecture of codec and implementation by VHDL.(harware)

- Verify on Arty-z7 FPGA(zynq) with vivado and vitis.(Embeded System)

- Under the 50MHz condition, after several improvements, the hardware resource consumption decreased from 938 LUTs to 843 LUTs. Meanwhile, the decoding latency reduced to 6 clock cycles, and continuous decoding became possible.

🔬 Research Experience

2024.11 - 2024.12, Research Assistant of 3D point cloud hardware (Remote)

-

Collaborate with Dr.Changchun Zhou(PhD@PKU & postdoc@DUKE)

- Design hardware acceleration units for 3D point cloud applications, include Farthest Point Sampling(FPS), AXI interface(Master/Slave).

- An energy-efficient acceleration chip supporting transformer-based networks and Fabricated in TSMC 28-nm HPC technology with an expected area of 2 mm×3 mm.

2023.10 - 2024.02, Neuromorphic Research Student

-

Eindhoven University of Technology, Netherlands

- I have completed the literature review on Neuromorphic Hardware Accelerator and Neuromorphic NoC.

- I have started architectural simulation using OpenSoC for the baseline NoC.

- Work in Eletronic System group with Prof. Manil Dev Gomony, Prof. Federico Corradi, and Prof. Henk Corporaal.

2021.10 - 2022.05, NoC Research Student

-

Institute of VLSI Design of HFUT, China

- Study the knowledge of Network-on-Chip(NoC) Router Based on Packet Connected Circuit(PCC).

- Implement the router and routing algorithm of PCC-NoC by using VerilogHDL.

- Verify it on FPGA and use UART(with FIFO) to communicate with PC.

- Use Python to verify result automatically.

- This project as my bachelor graduation project got A and advised by Zhenmin Li(HFUT).

🎖 Honors and Awards

- IEEE CAS Student Travel Grant, SOCC 2025

- Unergraduate Scholarship 2021/2022

📖 Skill

- Professional: Verilog/SystemVerilog/VHDL · FPGA · Lint · Linux · Cadence Tool(Xcelium,SimVision,Conformal Lint,Virtuoso,Genus,Innovus)

- Miscellaneous: Python · C/C++ · SystemC · MATLAB/Simulink · LaTex · CUDA · Pytorch · Perl/TCL/Shell · Git

- Language: Mandarian(Native), English