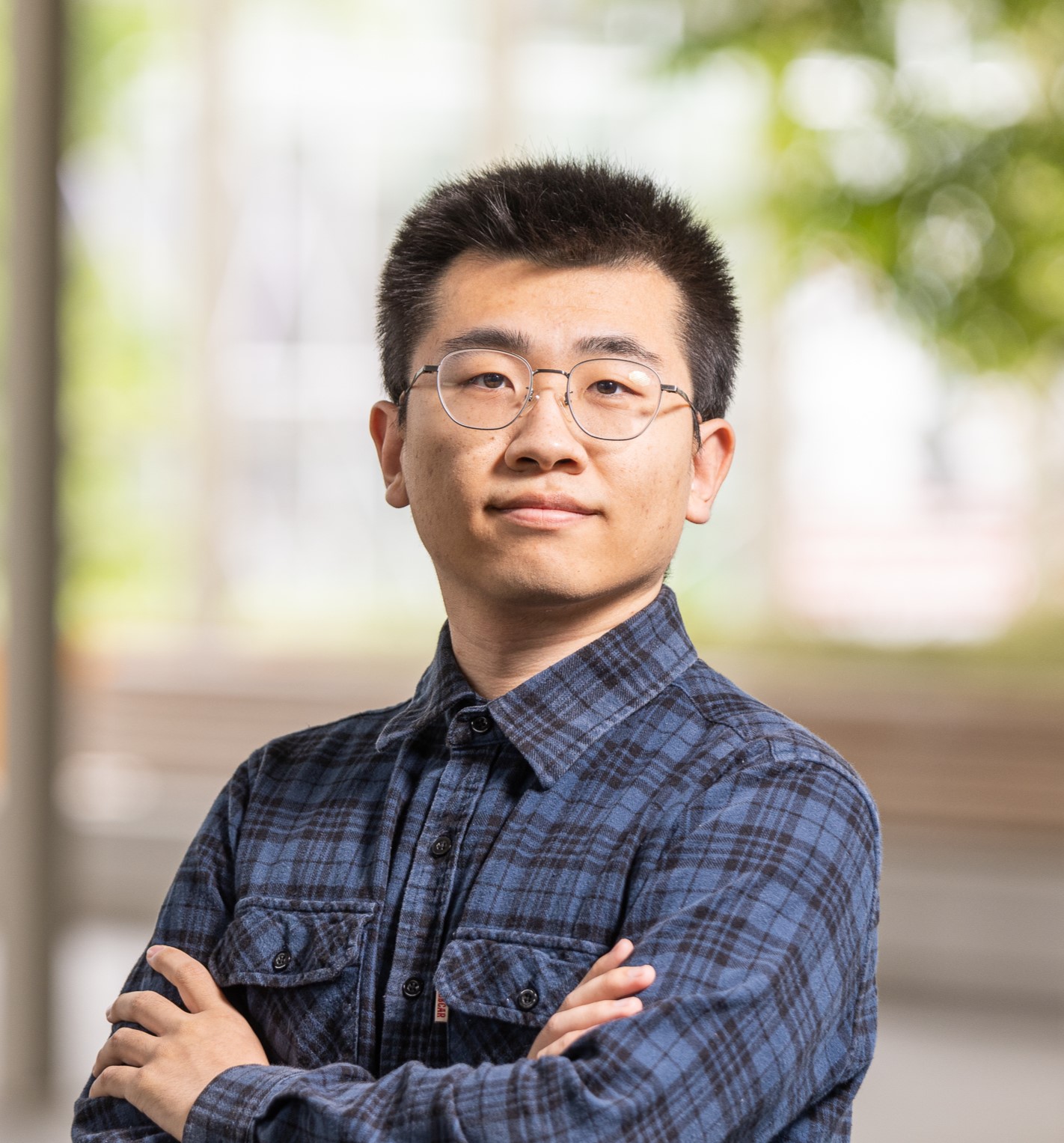

I am a second-year PhD student at University of Edinburgh (UoE), UK. I received my master's degree from Eindhoven University of Technology (TU/e), Netherlands, and my bachelor's degree from Hefei University of Technology (HFUT), China. My research focuses on digital hardware acceleration systems for large-scale AI models, with an emphasis on overcoming memory and computational bottlenecks through novel architectures. I am currently working on efficient hardware accelerators for LLMs, VLMs, and generative AI.

我目前是英国爱丁堡大学(UoE)工程学院二年级博士生,此前获得荷兰埃因霍温理工大学(TU/e)硕士学位,以及中国合肥工业大学(HFUT)学士学位。我的研究主要聚焦于面向大规模人工智能模型的数字硬件加速系统设计,希望通过新型体系结构缓解存储与计算瓶颈。目前的重点方向包括 LLM、VLM 以及生成式 AI 的高效硬件加速器。

Here is my CV. I am always open to research collaborations, so please feel free to contact me if my work resonates with your interests.

这里是我的 CV。我一直欢迎潜在的科研合作,如果你的研究方向和我的工作有交集,欢迎随时与我联系。

Open to opportunities: I am always interested in potential collaborations and open to research internship opportunities in both academia and industry. Please feel free to reach out via email.

开放合作与机会:我一直欢迎潜在合作,也对来自学术界和工业界的科研实习与合作机会保持开放。欢迎通过邮件与我联系。

Download my CV (Updated: May 2026)

下载我的简历 (更新于:2026 年 5 月)

News新闻

- [2026.04] I finished my first-year annual review.[2026.04] 我顺利完成了博士第一年的年度考核。

- [2026.04] I presented a poster and gave a two-minute talk on Towards Scalable GenAI Hardware Architectures with a Design Space Exploration Framework at the School of Engineering Research Conference 2026.[2026.04] 我在 School of Engineering Research Conference 2026 上展示了海报,并就 Towards Scalable GenAI Hardware Architectures with a Design Space Exploration Framework 做了两分钟口头介绍。

- [2026.03] I served as a teaching assistant for the Mini ASIC-BASIC Workshop and delivered a tutorial on Digital ASIC Flow in GF-22nm.[2026.03] 我担任 Mini ASIC-BASIC Workshop 助教,并讲授了 Digital ASIC Flow in GF-22nm 相关教程。

- [2026.02] I completed my first tape-out, Bent-Pyramid Systolic Array, in TSMC-180nm and served as a demonstrator for Digital System Laboratory 4.[2026.02] 我完成了第一颗流片芯片 Bent-Pyramid Systolic Array(TSMC-180nm),并担任 Digital System Laboratory 4 demonstrator。

- [2025.11] I attended Europractice's Advanced Node Digital IC Implementation course and received the certificate.[2025.11] 我参加了 Europractice 的 Advanced Node Digital IC Implementation 课程,并获得结业证书。

- [2025.10] I joined MeMRISYS 2025 in Edinburgh as a volunteer and served as a demonstrator for Digital System Laboratory 3.[2025.10] 我在爱丁堡以志愿者身份参加 MeMRISYS 2025,并担任 Digital System Laboratory 3 demonstrator。

- [2025.09] [Conference] I presented my work "LinkBo: a Single-Wire, Low-Latency, and Robust Protocol for Variable-Distance Chip-to-Chip Communications" at SOCC 2025 in Dubai, UAE.[2025.09] [会议] 我在阿联酋迪拜举办的 SOCC 2025 上汇报了论文 “LinkBo: a Single-Wire, Low-Latency, and Robust Protocol for Variable-Distance Chip-to-Chip Communications”。

- [2025.07] [Paper] Our work "LinkBo: a Single-Wire, Low-Latency, and Robust Protocol for Variable-Distance Chip-to-Chip Communications" was accepted by SOCC 2025 and selected for an oral presentation.[2025.07] [论文] 我们的工作 “LinkBo: a Single-Wire, Low-Latency, and Robust Protocol for Variable-Distance Chip-to-Chip Communications” 被 SOCC 2025 接收,并被选为口头报告。

- [2025.01] I started my PhD at the University of Edinburgh, supervised by Dr. Shady Agwa and Professor Themis Prodromakis.[2025.01] 我在爱丁堡大学开始博士学习,由 Dr. Shady Agwa 和 Professor Themis Prodromakis 指导。

- [2024.11] I finished my internship at NXP Semiconductors and successfully defended my master's thesis at TU/e with a score of 8.5/10. Committee members: Marc Geilen, Manil Dev Gomony, and Chengmin Li.[2024.11] 我完成了在 NXP Semiconductors 的实习,并在 TU/e 以 8.5/10 的成绩顺利完成硕士答辩。答辩委员会成员包括 Marc Geilen、Manil Dev Gomony 和 Chengmin Li。

- [2024.09] I received a conditional PhD offer from the University of Edinburgh.[2024.09] 我收到了爱丁堡大学的有条件博士录取。

- [2024.03] Congratulations to Intrinsic ID on being acquired by Synopsys.[2024.03] 祝贺 Intrinsic ID 被 Synopsys 收购。

- [2024.03] I moved my master's thesis to NXP Semiconductors in Nijmegen, supervised by Kimmo Salo and Gustavo Naspolini.[2024.03] 我的硕士论文课题转到奈梅亨的 NXP Semiconductors 完成,由 Kimmo Salo 和 Gustavo Naspolini 指导。

- [2023.11] I started working remotely as an Oversea VC Intern at Linear Capital.[2023.11] 我开始在 Linear Capital 远程担任海外 VC 实习生。

- [2023.10] I completed my internship at Intrinsic ID with a score of 8.5 and also started my neuromorphic hardware research at TU/e.[2023.10] 我完成了在 Intrinsic ID 的实习并获得 8.5 分,同时开始在 TU/e 开展神经形态方向研究。

- [2023.07] I joined Intrinsic ID for a 3.5-month internship, supervised by Rui Wang, Roel Maes, and Manil Dev Gomony.[2023.07] 我在 Intrinsic ID 开始了为期 3.5 个月的实习,由 Rui Wang、Roel Maes 和 Manil Dev Gomony 指导。

- [2022.09] I started my master's study at Eindhoven University of Technology (TU/e), The Netherlands.[2022.09] 我开始在荷兰埃因霍温理工大学(TU/e)攻读硕士学位。

- [2022.07] I graduated from Hefei University of Technology with a bachelor's degree, supervised by Zhenmin Li.[2022.07] 我从合肥工业大学本科毕业,由 Zhenmin Li 老师指导完成毕业设计。

Publications论文发表

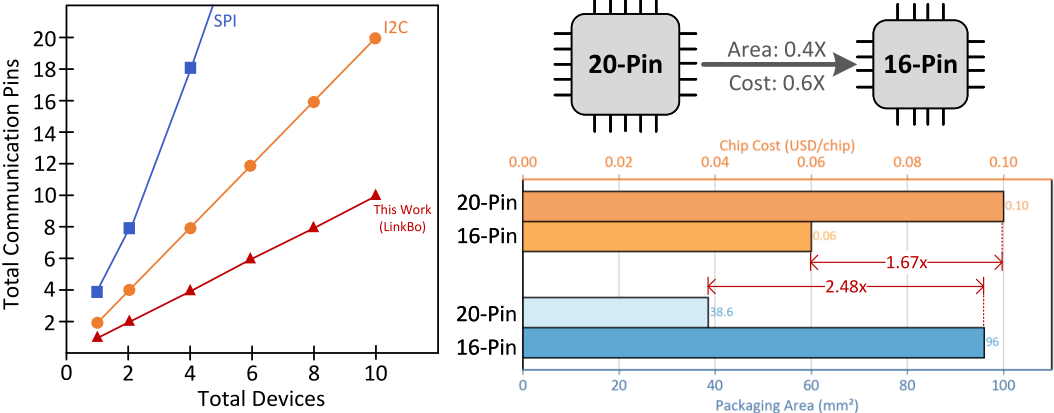

LinkBo: a Single-Wire, Low-Latency, and Robust Protocol for Variable-Distance Chip-to-Chip Communications

IEEE International System-on-Chip Conference (SOCC), 2025IEEE International System-on-Chip Conference(SOCC), 2025

Selected as Oral Presentation and Student Contest入选口头报告,并进入 Student Contest

Paper / Slides / Poster / ArXiv (Full Version) / Website

We propose LinkBo, a single-wire communication protocol with dedicated hardware architecture, designed to achieve low latency (50.4 us), high throughput (up to 7.5 Mbps @ 11 cm and 300 kbps @ 15 m), and robust priority-aware delivery.我们提出了 LinkBo。这是一种配套专用硬件架构的单线通信协议,能够实现低延迟(50.4 us)、高吞吐(11 cm 条件下最高 7.5 Mbps,15 m 条件下 300 kbps),并具备优先级感知的鲁棒传输能力。

Education教育经历

University of Edinburgh

PhD Student in Engineering工程学院博士生

Advisors: Professor Themis Prodromakis and Dr. Shady Agwa导师:Professor Themis Prodromakis 和 Dr. Shady Agwa

Research interest: Digital hardware accelerators for generative AI.研究方向:面向生成式 AI 的数字硬件加速器。

Eindhoven University of Technology

MSc Electrical Engineering, Electronic Systems Track电气工程硕士,Electronic Systems 方向

Thesis: LinkBo: A Robust Low-Latency 1-Wire Protocol for Chip-to-Chip Communications (8.5/10)硕士论文:LinkBo: A Robust Low-Latency 1-Wire Protocol for Chip-to-Chip Communications(8.5/10)

Hefei University of Technology

Bachelor in Integrated Circuit Design and Integrated Systems集成电路设计与集成系统本科

GPA: 83.1/100 (Top 22%)绩点:83.1/100(前 22%)

Thesis: The Research and Implementation of Router for Packet-Connect-Circuit Network-on-chip本科论文:The Research and Implementation of Router for Packet-Connect-Circuit Network-on-chip

Experience实习经历

NXP Semiconductors

Digital Design Intern数字设计实习生

Location: Nijmegen, The Netherlands地点:荷兰奈梅亨

Supervisors: Kimmo Salo, Gustavo Naspolini, and Manil Dev Gomony导师:Kimmo Salo、Gustavo Naspolini 和 Manil Dev Gomony

- A Robust Low-latency 1-wire Protocol for Chip-to-Chip Communications for PowerIC一种面向 PowerIC 芯片间通信的鲁棒低延迟单线协议。

Linear Capital

Oversea VC Intern海外 VC 实习生

Location: China (Remote, part-time)地点:中国(远程,兼职)

Mentor: Wei Xin, Songyan Huang导师:Wei Xin, Songyan Huang

Intrinsic ID (acquired by Synopsys) Intrinsic ID (被 Synopsys 收购)

IP Modeling and Digital IC Design InternIP 建模与数字 IC 设计实习生

Location: Eindhoven, The Netherlands地点:荷兰埃因霍温

Supervisors: Manil Dev Gomony, Rui Wang, and Roel Maes导师:Manil Dev Gomony、Rui Wang 和 Roel Maes

- Focus on a trellis-based Reed-Muller codec on FPGA for PUF IP.面向 PUF 的基于网格树结构的一阶 Reed-Muller 编解码器在 FPGA 上的实现。

Honors and Awards荣誉奖励

- IEEE CAS Student Travel Grant, SOCC 2025IEEE CAS 学生差旅资助,SOCC 2025

- Undergraduate Scholarship, 2021/2022本科生奖学金,2021/2022 学年

Skill技能

- Professional: Verilog / SystemVerilog / VHDL, FPGA, Lint, Linux, Cadence tools (Xcelium, SimVision, Conformal Lint, Virtuoso, Genus, Innovus)专业技能:Verilog / SystemVerilog / VHDL、FPGA、Lint、Linux,以及 Cadence 工具链(Xcelium、SimVision、Conformal Lint、Virtuoso、Genus、Innovus)

- Miscellaneous: Python, C/C++, SystemC, MATLAB / Simulink, LaTeX, CUDA, PyTorch, Perl / TCL / Shell, Git其他技能:Python、C/C++、SystemC、MATLAB / Simulink、LaTeX、CUDA、PyTorch、Perl / TCL / Shell、Git

- Language: Mandarin (native), English语言:中文(母语)、英文